Rotor Synnchronization 轉子同步法:

1.感測器法; Hall sensor

2.無感測器法:反電勢,分析未驅動相的反電勢訊號,證實交換點(換相點)

轉子速度調整

1.閉迴路控制:可針對'最終的負載變動做速度補償

2.開迴路控制:在BLDC同步驅動器不需要做到速度控制,轉子最終速度會受負載變動影響

匯流排電壓'調整

1.電流模式:透過'PWM信號設定電流準位以及使用外部RC濾波器設定比較門檻,控制變數是每相電流

2.電壓模式:控制變數是每相電壓,經由固定PWM訊號的DUTY CYCLE,以達到電壓調整.電流限制的級別可由外部電阻分壓決定或經由PWM訊號濾波器(RC電路)

轉子速度測量:

依據公式RPM=(反電勢頻率*60*2)/轉子極數

藉由兩個連續的反電勢零交越以計算]時間的延遲稱為單位時間量測STEP TIME

通訊延遲和消磁時間:

通訊延遲約為一半的step time區間約落在zero crossing 以及step time commution之間

BEMF 只能在未驅動的那一像電流為流才可量測

零交越偵測:

在切換PWM過程中(未驅動相那一相)

T-ON :上臂有效時, 中性點為1/2 BUS電壓

T-OFF:下臂有效時,中性點為零 .

動態反電勢取樣:

這方法針對在低速的低duty cycle以及高速的100% duty cycle最小的反電勢分割

標準BLDC啟動程序有兩種組成:

1.The Alignment phase (校準相):再此模式時,驅動馬達前轉子需移動至指定位置,而要進行此動作.六相開關需設某一組態,令轉子先至某一固定位置,例如:step 6->step 1,下一個要換相的動作是step時,需先移至step 6位置.

2.The ramp-up phase (爬升相):主要功能是執行加速馬達到可以判斷反電勢的速度.當轉速達到的速度可察覺反電勢時,這同步機制視為有效.此機制也稱為自動變換模式.

2013年12月12日 星期四

MAX232 通訊異常現象

在以轉接版的方式與外部進行溝通發現個問題.

如果V+ 與V- 電位不足時,在與外部溝通的DOUT(TX)會有無訊號現象產生.

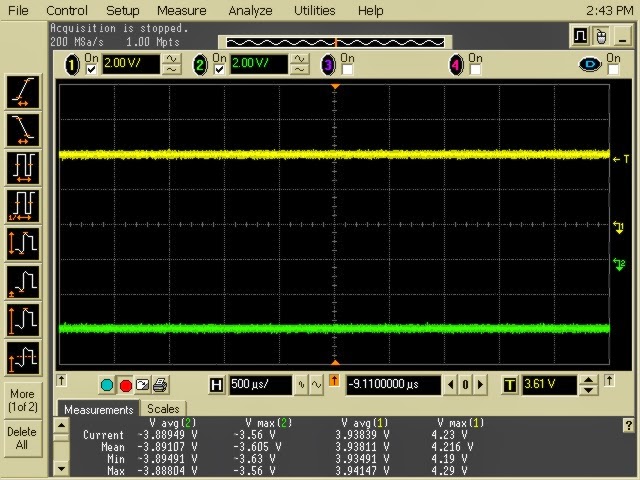

下圖是正常可通訊下,V+ & V-的電位,都可達到正或負7v左右.

下圖是無法通訊時,V+ &V- 電位,大概都與電源準位差不多等級.

如下圖是MAX232(or max3232)的第13腳所量到的波形.針對此種情況如果以同一台PC做通訊測試,記錄到的波形是完整的方波

但是如果用不同設備做溝通時,第13腳所量到的波形.

一開始認為是電容匹配問題,一直修改都沒改善,之後又去試著另外加一顆LDO以及在電源回路上加BEAD甚至在第13PIN並聯電阻以及電容.

到最後發現到問題是共地沒處理好!後來在溝通用的線材中把沒使用的線多拿一路來做地線.才解決問題!!

2013年12月3日 星期二

Labview 基本認識

啥叫vi??

虛擬儀表 (virtual instrument): 簡稱 VI,是以 LabVIEW 語言撰寫之程式,其儲存的副檔名為 .vi。其格式如同是右上圖,是由使用者使用的人機介面 (front panel) 與程式設計者使用的程式方塊 (block diagram) 兩個視窗所組成

sub vi??

次程式 (sub-virtual instrument): 簡稱 sub-VI,每一個 VI 內還可以包含許多次程式,這種次程式就叫做 sub-VI。更正確的說法是 sub-VI 是將 VI 設計成許多通用程式 (universal program),在撰寫 VI 時可利用這些 sub-VI 來組裝成一個適合個人的 VI 來使用,而不需要一再地重複的撰寫程式,是程式中的程式。

請參考http://www.pt.ntu.edu.tw/hmchai/hLabVIEW/LVintroduction.htm

Labview 建立DLL檔或執行檔的方法:

當專案已建立完,請在 project explorer視窗中在Build Specification按右鍵選New,之後會有一堆可產生的檔案類型供選擇

虛擬儀表 (virtual instrument): 簡稱 VI,是以 LabVIEW 語言撰寫之程式,其儲存的副檔名為 .vi。其格式如同是右上圖,是由使用者使用的人機介面 (front panel) 與程式設計者使用的程式方塊 (block diagram) 兩個視窗所組成

sub vi??

次程式 (sub-virtual instrument): 簡稱 sub-VI,每一個 VI 內還可以包含許多次程式,這種次程式就叫做 sub-VI。更正確的說法是 sub-VI 是將 VI 設計成許多通用程式 (universal program),在撰寫 VI 時可利用這些 sub-VI 來組裝成一個適合個人的 VI 來使用,而不需要一再地重複的撰寫程式,是程式中的程式。

請參考http://www.pt.ntu.edu.tw/hmchai/hLabVIEW/LVintroduction.htm

Labview 建立DLL檔或執行檔的方法:

當專案已建立完,請在 project explorer視窗中在Build Specification按右鍵選New,之後會有一堆可產生的檔案類型供選擇

變壓器漏感對Vds的影響

一般我們常常聽說變壓器漏感要小ㄧ點,要不然MOSFET上的voltage spike會很高,但會多高呢?我們希望透過計算的方式來了解。這邊我們以flyback converter為例子。

首先我們先針對沒有緩衝線路來做計算,這時候對於voltage spike的影響,除了漏感外就只有MOSFET的Coss,在MOSFET turn off的時候,儲存於漏感上的能量為1/2LI^2,此時由於MOSFET已經open了,所以這能量會透過MOSFET的Coss做放電,所以儲存的能量=1/2(Coss)V^2,V即為我們看到的voltage spike,所以Coss越大則會得到較小的voltage spike。

我們以實例來做說明,當我們設計一個變壓器感量為450uH而漏感是10uH時且透過計算後I peak=5A,MOSFET turn off 時漏感儲存的能量是1.25*10^-4=0.5*C*V^2

如果使用的MOSFET的Coss為1000pF,則voltage spike=500V,所以我們需要另外使用緩衝電路來降低voltage spike,同樣的道理,緩衝電路的C越大則voltage spike越小。

但我們常看緩衝電路會有併聯一個電阻,這個電組主要作用是要確定C有放完電,這樣再下一個週期C才能發揮其作用,所以當R大到一定程度C會失去作用。

這裡放電時間可以用T=RC來計算。

switch power supply snubber circuit 學習經驗

之前主管開發的電源板,出現了個小問題.也就是有些版子在240V以上的供電電壓無法正常輸出.

經過快兩個月的電路了解,發現了幾個可改善的點,不外乎是更動變壓器以及mos fet 或者snubber 要更改.

以下就針對snubber的部分記錄.

電源板中可稱為snubber的,有三個部分.變壓器一次側,變壓器二次側,以及與MOS FET 並聯的電容.

首先說明MOSFET並聯電容,因為選用的電源IC是使用諧振技術,所以會和變壓器的電感,一次漏感以及MOS FET的Coss有關.漏感一般來說小會比較好,在變壓器方面可用三明治繞組方式降低漏感.

而當功能都正常以後,就要來看是否會有EMI的問題產生.

例如:在mosfet 旁並電容,emi可能會過但是供電電壓超過某個數值後,電路就不正常.

但是不並電容在高電壓也許可正常輸出電壓,可是emi又超標.

再來說明變壓器一,二次側的snubber

建議可以參考http://www.deyisupport.com/cfs-file.ashx/__key/telligent-evolution-components-attachments/00-24-01-00-00-06-00-97/snubber-design.pdf

二次側snubber的部分

我一開始先看看沒有snubber時的波形周期,然後在依建議事項加電容讓波形變成兩倍周期.

下圖是未加snuber的二次測波形,周期約42nS

下圖設計是使用2.2nF未加電阻的波形, 周期約101nS

而如果用1nF未加電阻,周期看來是90nF.所以不管哪個都和建議的兩倍周期差不多,那容值還是用2.2nF.

在來嘗試去更動電阻,下圖波形為一開始設計使用33 ohm配2.2nF.

後來依公式算出以10 ohm去測試,高電壓還是不工作.

一直測到以33k ohm高電壓才可正常工作.可是波形有明顯震盪看來會影響EMI.

下圖是1K ohm下的波形

PS:高壓和低壓的波形 二次測的波形都是一樣.所以在低壓下解就可以了.

經過快兩個月的電路了解,發現了幾個可改善的點,不外乎是更動變壓器以及mos fet 或者snubber 要更改.

以下就針對snubber的部分記錄.

電源板中可稱為snubber的,有三個部分.變壓器一次側,變壓器二次側,以及與MOS FET 並聯的電容.

首先說明MOSFET並聯電容,因為選用的電源IC是使用諧振技術,所以會和變壓器的電感,一次漏感以及MOS FET的Coss有關.漏感一般來說小會比較好,在變壓器方面可用三明治繞組方式降低漏感.

而當功能都正常以後,就要來看是否會有EMI的問題產生.

例如:在mosfet 旁並電容,emi可能會過但是供電電壓超過某個數值後,電路就不正常.

但是不並電容在高電壓也許可正常輸出電壓,可是emi又超標.

再來說明變壓器一,二次側的snubber

建議可以參考http://www.deyisupport.com/cfs-file.ashx/__key/telligent-evolution-components-attachments/00-24-01-00-00-06-00-97/snubber-design.pdf

二次側snubber的部分

我一開始先看看沒有snubber時的波形周期,然後在依建議事項加電容讓波形變成兩倍周期.

下圖是未加snuber的二次測波形,周期約42nS

下圖設計是使用2.2nF未加電阻的波形, 周期約101nS

而如果用1nF未加電阻,周期看來是90nF.所以不管哪個都和建議的兩倍周期差不多,那容值還是用2.2nF.

在來嘗試去更動電阻,下圖波形為一開始設計使用33 ohm配2.2nF.

後來依公式算出以10 ohm去測試,高電壓還是不工作.

一直測到以33k ohm高電壓才可正常工作.可是波形有明顯震盪看來會影響EMI.

下圖是1K ohm下的波形

PS:高壓和低壓的波形 二次測的波形都是一樣.所以在低壓下解就可以了.

訂閱:

意見 (Atom)