2012年9月3日 星期一

I2C logic level不足問題

1.傳輸率有標準模式100Kbit/s,快速模式400kbit/s,進階快速模式1Mbit/s,高速模式3.4Mbit/s

2.SDA & SLK logic level VIH=70% of VDD, VIL=30% of VDD,特別注意有些舊的i2c標準的裝置

也許會要求固定VIL=1.5V,HIH=3.0V, 依照新I2C標準的裝置基本上還是以30% 以及70%為準

3.SDA 資料的有效性,是只有在SLK為HIGH的週期狀態下,才有參考性質如下圖

Master:Stm32f103rc

Slave:Honeywell HAF series sensor

Power :3.3V

digital interface:I2C

IO模擬i2c 並設為開集極方式

使用I2C介面 SDA&SLK會加上4.7K的提升電阻 master&slave 的SDA&SLK 會個別接一起

空接測量 SDA阻抗為3.2K ,SLK阻抗為342K

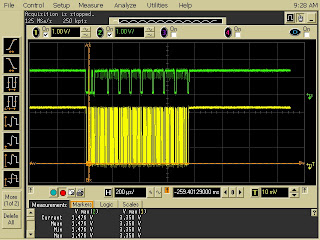

遇到如下狀況:黃色為SLK,綠色為SDA

1.加上提升電阻4.7K並斷開Master端連結,波形如下

2.加上提升電阻4.7K並斷開Slave端連結,波形如下

3.加上提升電阻4.7k,Master & slave通訊波形

4.單純供電給slave 不加上提升電阻

向FAE反映 SDA對地阻抗為3.2K ,是為了防干擾

所以建議使用1K~800 Ohm的提升電阻,而加上此提升電阻值後,

電壓有提升到 2.4V

如果爲了SDA要到3.3V,可試著在5V加上1.6K的提升電阻再接到SDA上 ,就有3.3V了

經過測試訊號可正常運作.

額外做了以下測試,依照AN97055 BI-directional level shifter for I2C-bus and other systems

電路如下

實際接線後,slave端還是會因為logic level 太低 無法回應

建議可用以下電路,令slave端的電壓可以達到3.3v

訂閱:

張貼留言 (Atom)

沒有留言:

張貼留言